Release 2022 R1 Highlights

Signal & Power Integrity

**Slwave**

**Ansys**

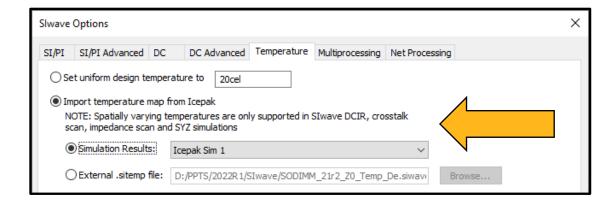

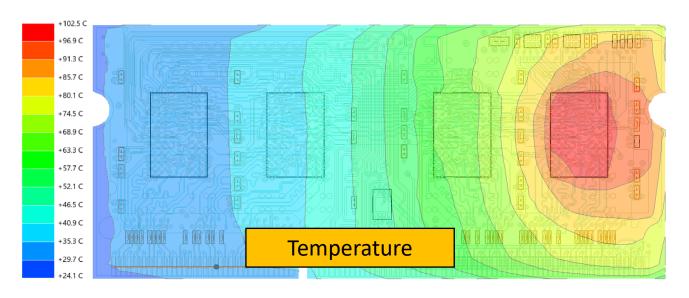

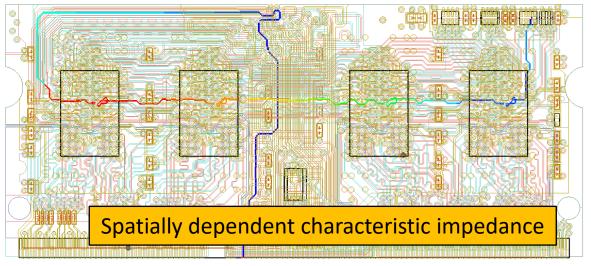

### Temperature dependent materials in Slwave AC

- Temperature map import from Icepak

- Thermal modifier applied to dielectric materials and conductors

- Non-uniform temperature distribution supported

- Spatially dependent permittivity and conductivity for plane (FEM) and trace (MoM) models

#### Temperature dependent materials in Slwave AC 600.00 Ansys Insertion Loss 500.00 Forced convection -12.50 -25.00 -37.50 -50.00 300.00 200.00 Curve Info Forced\_convection -62.50 0.00 2.00 6.00 10.00 Freq [GHz] 600.00 Insertion Loss Ansys **Natural convection** 500.00 -12.50 400.00 300.00 -25.00 , ≿ <sub>-37.50</sub> 200.00 Curve Info -50.00 100.00 Forced\_convection -62.50 Natural\_convection 2.00 4.00 6.00 8.00 10.00 Freq [GHz]

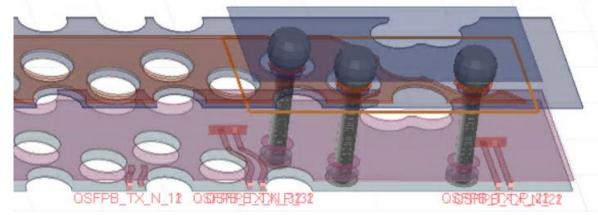

### **SIwave HFSS Regions**

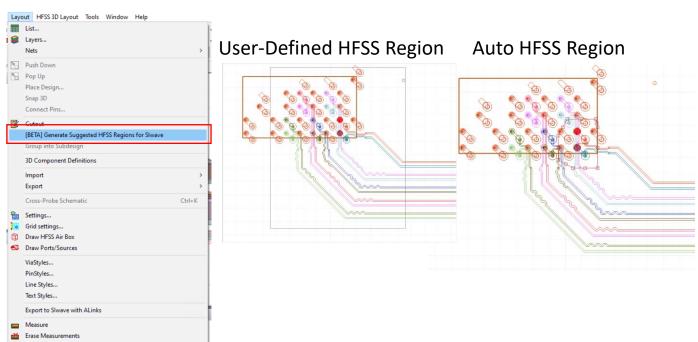

# [BETA] Auto (suggested) SIwave HFSS Regions in 3D Layout

- Creates HFSS Regions around areas of significant

3D activity

- Guarantees Electrical Coherence for HFSS Simulations

- Regions are a suggestion; users can modify or remove regions they dislike

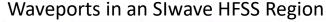

### [BETA] EDB-based Region Clipping

- When launched from 3D Layout, replaces ClipDesign during preparation HFSS Regions

- Operates directly on an EDB, preserving EDB-only elements such as waveports

- Activate through Beta Feature

### **SIwave HFSS Regions**

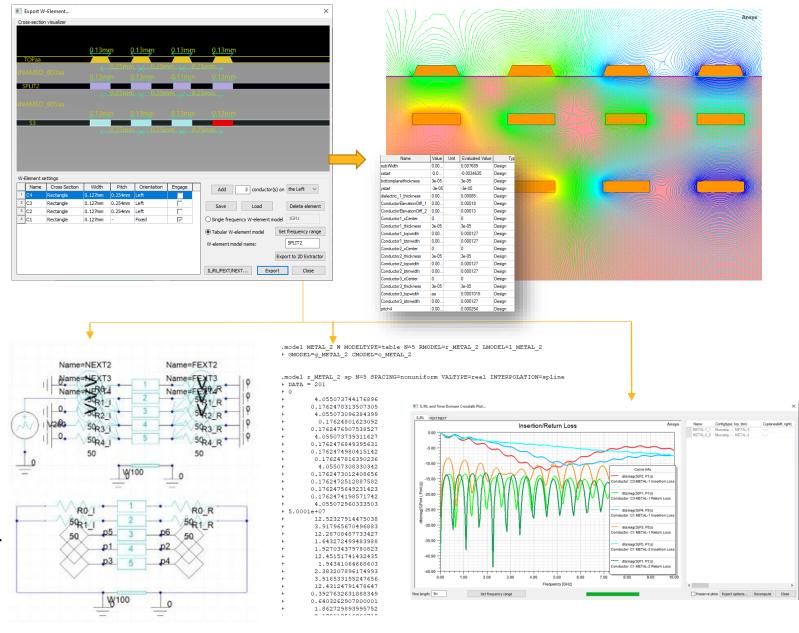

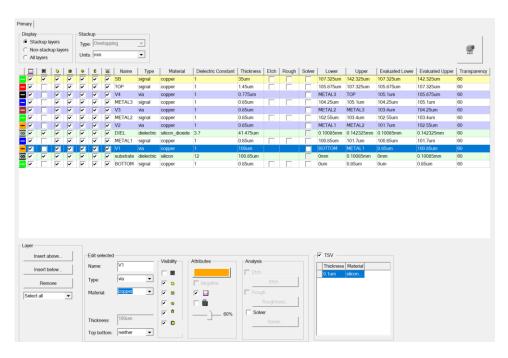

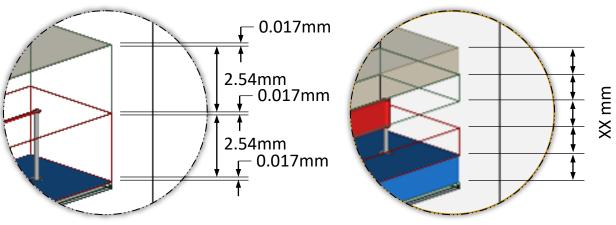

# Stackup Wizard

- Ability to define/engage multiple conductors in one simulation

- Multiple ports for linear network analysis

- Multiple victims for cross talk analysis

- Engage multiple conductors across selected layers

- Fully parameterized 2D extractor export

- Conductor pitch/width/thickness/etch

- Conformal, dielectric, signal layer thickness and elevation

- Circuit schematic and Touchstone file export supports multi-layer conductor models

- Supported in W-element cross section analysis feature in Slwave and 3D layout

- Available in Slwave, 3D Layout, SIXplorer

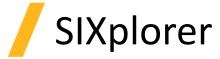

#### Via Wizard

- Freeform stitching via placement

- Stitching via location is defined using placement radius and angle

- Support copy/paste of entire grid row to add new definition

- Allow bulk updates to values of placement radius and angle by clicking on corresponding column header

- Addition of 2D top-down EDB preview in via configuration dialog

- Two-way selection between grid row and 2D view

- Propagate synthesized/analyzed trace width/pitch from Impedance wizard to Via wizard

- Allow import of stackup and padstacks from unsourced/non-SIXplorer AEDT projects/EDBs

#### Impedance Wizard

Ability to save/restore UI state at application close/launch

# **EMI** Scanner

- Rule-checking Improvements

- Use more appropriate distance metrics in various rules

- Proper handling of curved traces

- Edge-to-edge vs center-to-center

- Distribution of vias over grid rather than just simple count

- Additional details and images in exported reports

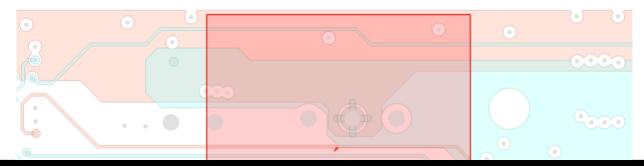

#### **EMI Violations**

Rule Type: Signal Reference

Rule Name: Critical Net Crossing Split Reference Plane

Rule Description: Critical nets must not cross a split in the adjacent reference plane. Notes: 1. Any crossing of an adjacent plane by a critical net will c

Rule Description: Critical nets must not cross a split in the adjacent reference plane. Notes: 1. Any crossing of an adjacent plane by a critical net will cause a violation. 2. A crossing is allowed if two stitching capacitors (one on either side of the crossing point) are within a specified distance of the crossing.

Violation 1: Cap Search Box = [(23.622, 5.1.302)] 38.862, 66.3702], Gap Point = (31.242, 58.7502). Net = AQ\_GPIO. Reference Layer = LYR\_1, Signal Layer = LYR\_2.

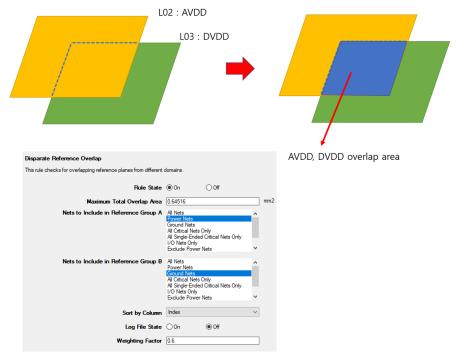

- New Rule: Disparate Reference Overlap

- Requested for CMOS image sensor development

- Power supply noise sensitive to coupling of digital reference and analog reference

- Define a set of nets whose planes cannot overlap with planes from the other set

- Violations issued if total overlap area exceeds a threshold

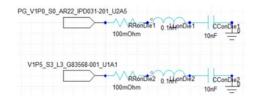

# DDRwizard

- Schematic organized in multiple tabs

- Main tab contains dynamic-link block along with driver/receiver components

- Nets grouped by byte lanes with corresponding strobe

- Separate tab for IBIS blocks

- OnDie RLC support for VRM nets

New tab for ADDR/CLK/OTHER nets in IBIS assignment dialog

DDR schematic organized into logical tabs

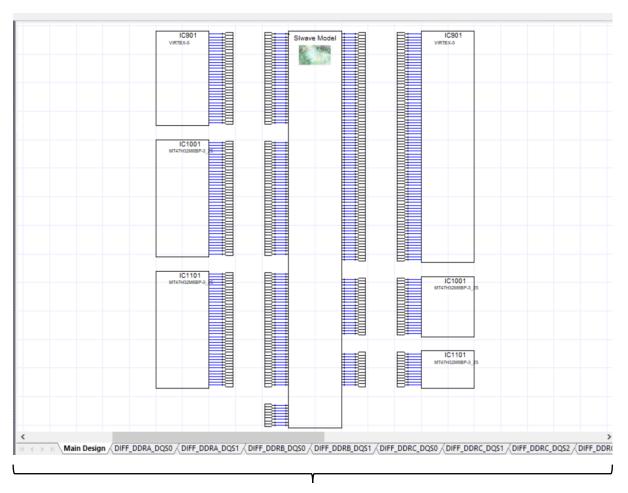

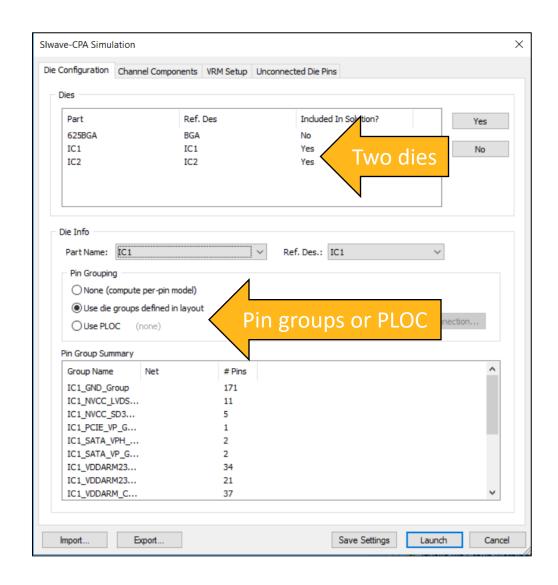

### CPA Solver

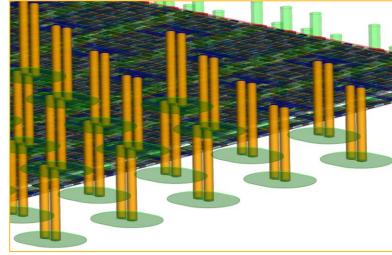

- Multi-Die and Multi-PLOC support

- Extract RLCG for multiple dies

- Import and connect PLOC/CPM or set the Pin Grouping model for each die individually

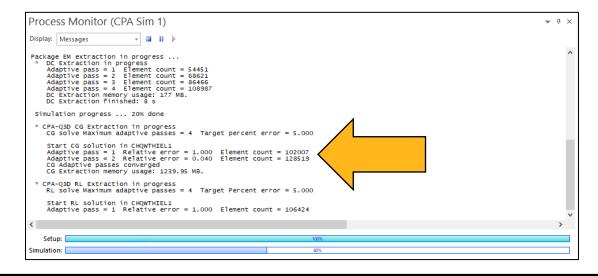

- Adaptive process update and messaging in real time for CPA-Q3D solver

## CPA Solver

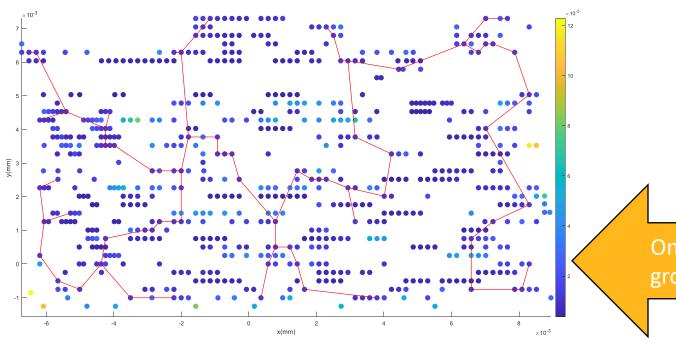

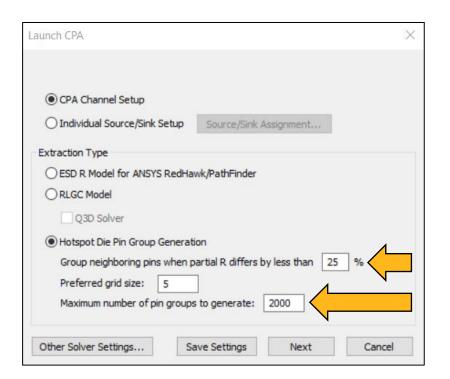

- Smart pin group enhancements

- Cluster-based pin grouping algorithm with user-specified percentage ( $\Delta R$ ) maximum pin group number

One connected pin group on colormap

- PLOC to smart pin group matching

- Apply hotspot pin groups to die components by preserving the PLOC connectivity data

**Q3D Extractor**

**Ansys**

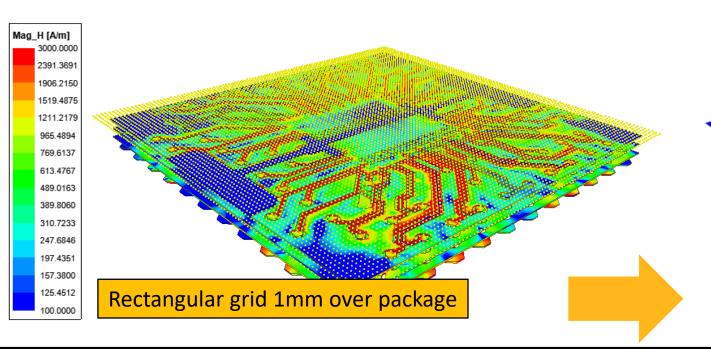

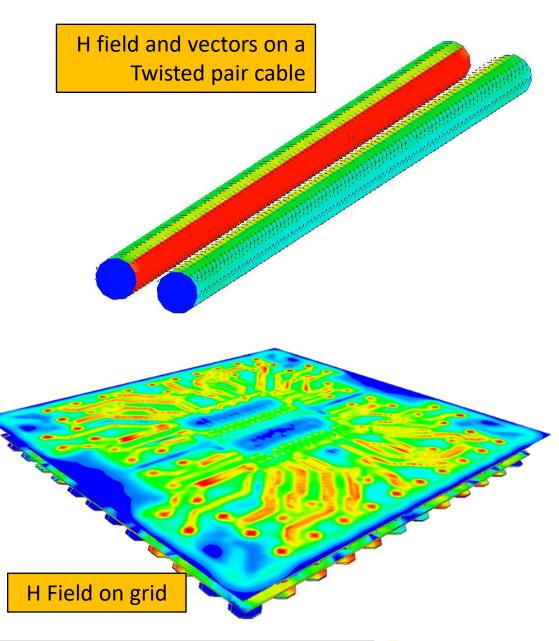

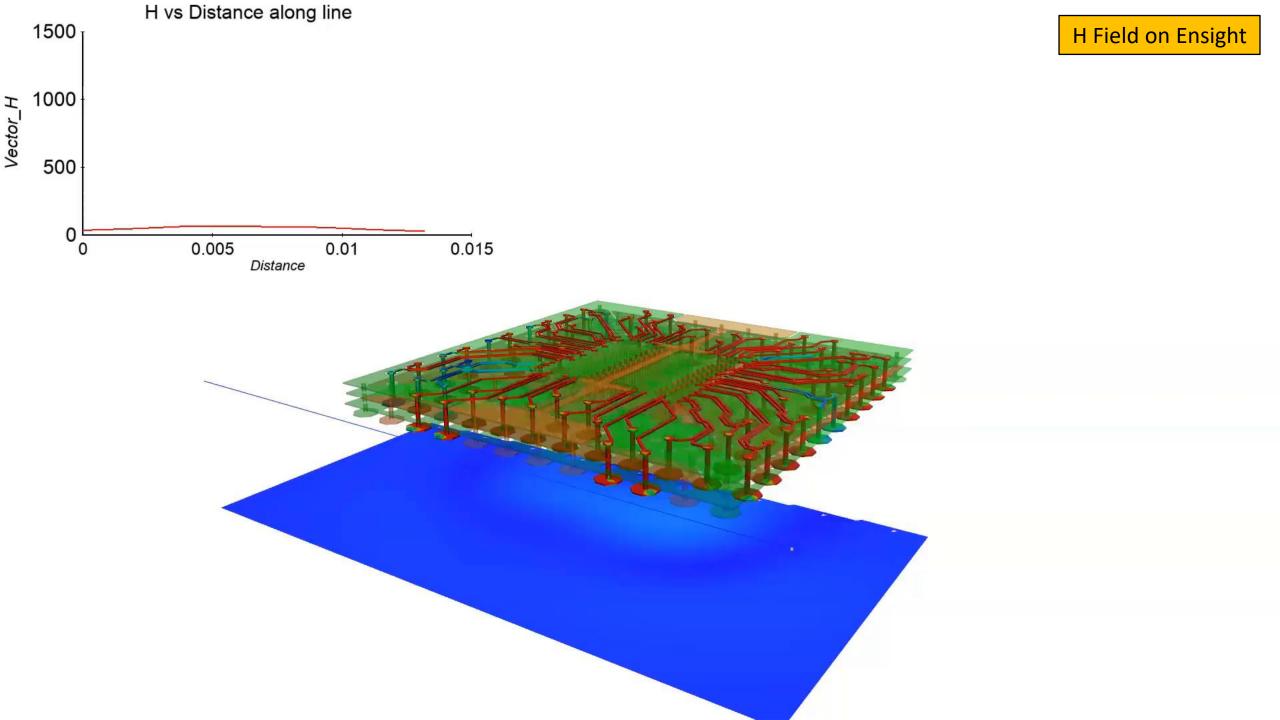

### Magnetic field visualization for AC-RL

- Support H field overlay and export to Ensight

- Support H field report on user defined EM fields setup

- Box, Line, Rectangle, Sphere

- 2D contour plot overlay to modeler window

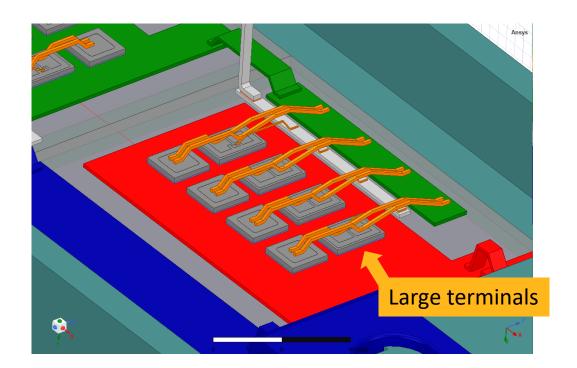

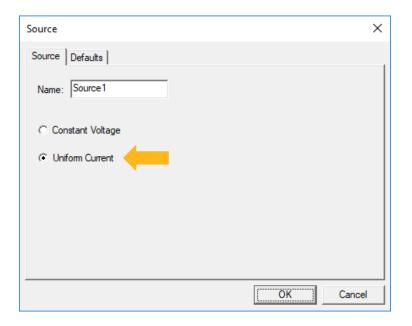

# Uniform current terminals for AC-RL and DC-RL

- Released uniform current terminals for the DC-RL solver

- Uniform current and constant voltage terminals can coexist

- Required for modeling power modules

- Adding additional terminals will not impact the inductance

**Circuit**

**Ansys**

#### Multiple TDR Probes

- Improved behavior of Circuit when multiple TDR probes are used.

- Provides better accuracy for coupled channels.

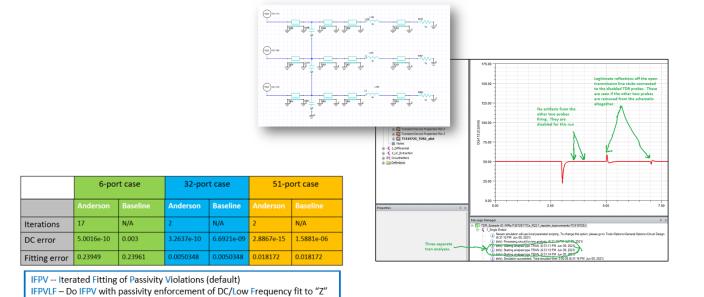

- Passive DC Fit Enhancement for "IFPVLF"

- Enforce passivity sometimes destroys the fit at low frequency/DC.

- The new "IFPVLF" DC passivity enhancement with Anderson Acceleration improves the DC passive fit of "IFPVLF".

- Now (R22.1) a full feature in both Nexxim and NDE including Nport and Dynamic Link (DL)

- Dynamic Link Frequency Sampling Points for Circuit-Field Solver CoSim [Beta]

- Previously, the exact sweep, discrete or interpolating, S-data calculated by the field solver was not used by Circuit - Circuit chose its own set of discrete 501 uniform samples between DC and maximum.

- This 22.1 beta feature ensures that the user specified sweep S-data is being passed to Circuit for state-space fitting.

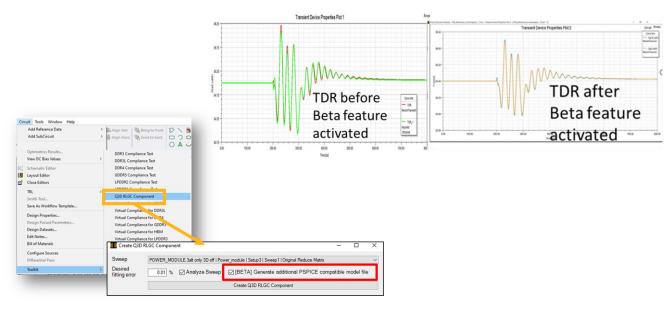

- PSPICE Model Export for Q3D RLGC State-Space Fitting [Beta]

- "Q3D RLGC Component" Circuit toolkit introduced at 2021 R2.

- Creates Circuit component based on state-space fitting of Q3D RLGC data for improved accuracy in many power electronics applications.

- The toolkit can now export a PSPICE-compatible model file.

### **Network Data Explorer**

#### NDE Scripting [Beta]

- Added script commands to oNDE = oDesktop.GetTool("ndExplorer")

- Postprocessing: renormalization, deembeding, differential pairs

- Transforms: all supported SPIsim transforms, Smoothing, Termination

- HasSameData function to compare data from two NetworkData objects

- Documentation is in place

- Released as Beta because some commands may change in the future

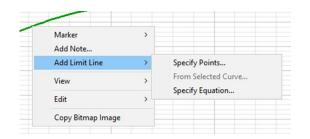

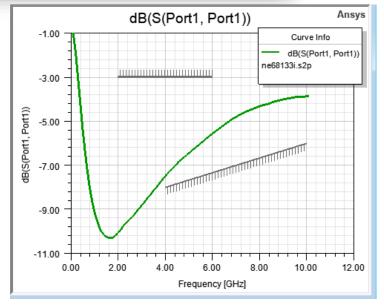

#### Limit Lines

- Associated with a particular network data and matrix entry, e.g. S11

- Persistent until the network data is closed or AEDT closes

#### **Circuit Scripting Guide**

#### **Network Data Explorer Script Commands**

Network Data Explorer (NDE) scripting uses three objects, each with unique script commands:

- Network Data Explorer top-level object obtained by calling oNDE=oDesktop.GetTool("ndExplorer"). network data Explorer commands are called using oNDE.

- Network Data single set of S-parameters, corresponding to a single entry in the UI tree.

Network Data commands are called using oData.

- Post Process Settings settings that can be applied and removed from network data without

making permanent changes to the underlying data. Post Process Settings commands are called

using perstage.

Examples using the above objects:

```

oNDE = oDesktop.GetTool("ndExplorer")

oData = oNDE.Open("D:\folder\test.s2p")

success = oPostProc.AddDiffPair(2, 1, "Diff1", "Comm1", 100, 25)

```

#### State Space Model Support

- .sss reading is now supported in all of SPISim's viewer/sparam infrastructure.

- SPISim's waveform and all S-param related analysis, including COM, can now take .sss file as input for processing.

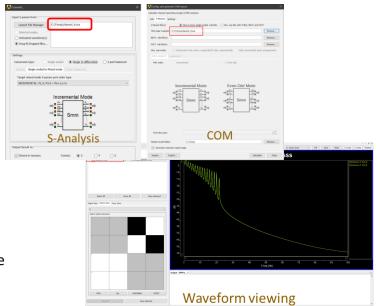

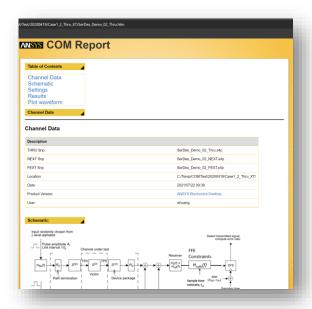

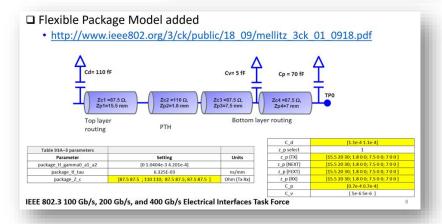

#### Expose SPISim COM Outputs in AEDT [BETA]

- Support COM directly via AEDT's toolkit:

- Generate summarized reports with all settings, results and plots in one place/page.

- Also includes a waveform viewer for exploring interactively.

- Allows users to utilize SPISim's COM analysis capabilities much more directly with integrated look & feel and reports.

- Run COM in non-gui (NG) batch mode

- Customized flow and analysis

- Optimization (iterative)

C:\Program Files\ansysEM\v221\win64\spisim\spisim\modules\ext>SPISimJNI\_WIN64.exe COM -v CFGFILE=C:/Temp/COM/T est/20200419/case1\_2\_Thru\_XT/TestERL.cfg [INFO]: Executing SPISimJNI in NON-GUI mode... |Parmbati: COM=-5.6351 -6.7771.II\_D=0.5317 0.5317.ICN=3.9362 3.9362.ERL=18.5110 18.5110

- SPISim COM implementation updated to reference ver. V2.57

- COM can now support 802.3cd and 802.3ck specs.

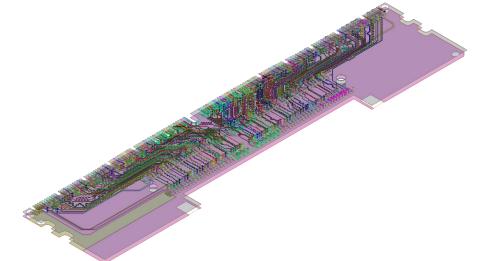

**HFSS 3D Layout**

**Ansys**

### IC and GDS Workflow

- Geometric/simplification functions

- Add "convert to circle" (UI and XML)

- Critical-net based hole removal in GDS processing (XML)

- Support metal layer union (UI and XML)

- Workflow and setup automation

- Preview stackup from GDS import dialog

- Import ports from csv file in GDS import dialog

- Net tracing display/improvements in GDS import dialog

- Enable port referencing to closest pin on a net (XML)

- Improve pin creation based on points (XML)

- Improve auto-component creation (XML)

- Support relative path for component models (XML)

- Use polygons on layer to create seeding-by-region operation (XML)

- Create shapes on metal layer (XML)

- Modeling features

- Solve-inside by region

- Add TSV option to via layer (UI and XML)

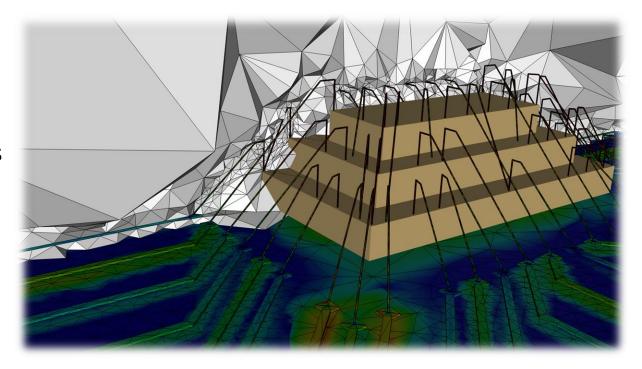

### Mesh Fusion Usability

- Phi+ available for Mesh Fusion [Beta]

- Only for the top-level and Layout sub-designs

- Improved meshing for assemblies with Phiincompatible domains

- Assemblies with bondwire packages

- PCB's with connectors

- Domains hosting complex envelopes

- Intersection check performance

- Robustness

- Improved pre-processing

| Initial Meshing                             |          |          |        | Time: 08/13/2021 10:24:52                  |

|---------------------------------------------|----------|----------|--------|--------------------------------------------|

| Initial Mesh With Distributed Mesh Assembly |          |          |        |                                            |

| Mesh Phi                                    | 00:09:51 | 00:09:51 | 8.18 G | 1881059 tetrahedra [U1]                    |

| Mesh (MRL based)                            | 00:02:46 | 00:02:45 | 8.23 G | 1912366 tetrahedra [U1]                    |

| Phi Plus                                    | 00:15:28 | 00:26:21 | 7.38 G | 4533487 tetrahedra [native] by 24 of cores |

| Mesh Coarsening                             | 00:07:41 | 00:07:41 | 7.38 G | 3345911 tetrahedra [native]                |

| Mesh Assembler                              | 00:30:39 | 00:30:39 | 7.25 G | 0 tri + 5258277 tets                       |

| Refinement With Distributed Mesh Assembly   |          |          |        |                                            |

| Mesh Assembler                              | 00:04:11 | 00:04:11 | 4.63 G | 0 tri + 5208808 tets                       |

| j.                                          |          |          |        |                                            |

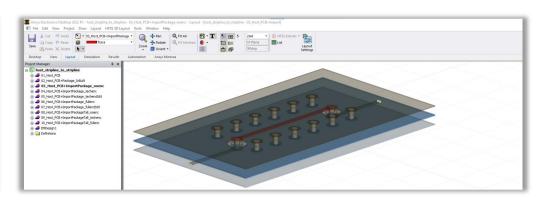

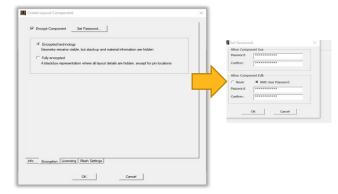

### 3D Layout Component (Beta)

- Layout Component

- Any EDB can function as a component

- Encapsulated data handling

- Encrypted Technology

- Obfuscated stackup

- No material definitions available

- All data/mesh/solutions encrypted on disk

- Fully Encrypted

- Blackbox view

- Visibility of terminal locations only

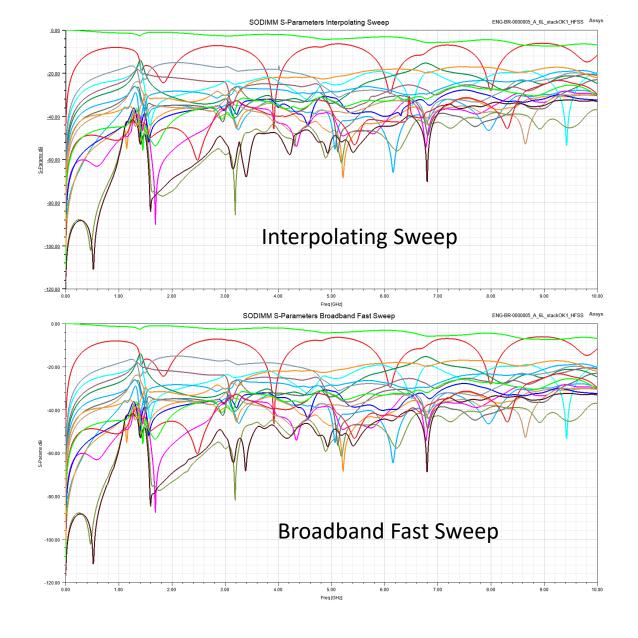

### **Broadband Fast Sweep (Beta)**

- Projection-based model order reduction

- Uses derivatives of solution vectors as basis.

- Uses automatic differentiation for derivatives of causal dielectrics, finite conductivity BC, etc.

- Excellent accuracy with fewer basis points

|                | Time         | Basis points | Speed |

|----------------|--------------|--------------|-------|

| Interpolating  | 3 hr, 50 min | 113          | 1     |

| Broadband Fast | 2 hr, 8 min  | 24           | 1.79  |

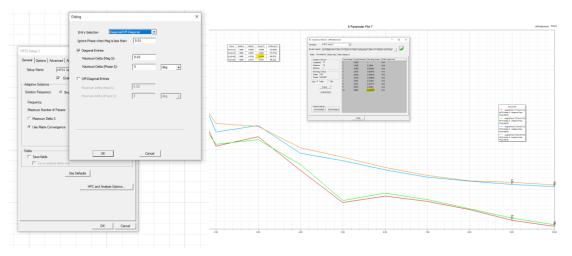

### Layout Usability Enhancements – 2022R1

- New convergence criteria support

- Matrix

- Output variables as functions of Differential Pairs

- 3D Component Display in Project Tree

- Selection, Edit Definition, Edit Properties, Visibility

- Fields Post-Processing

- Volume loss density

- 3D-Line types available for Fields Calculator

- Performance improvements

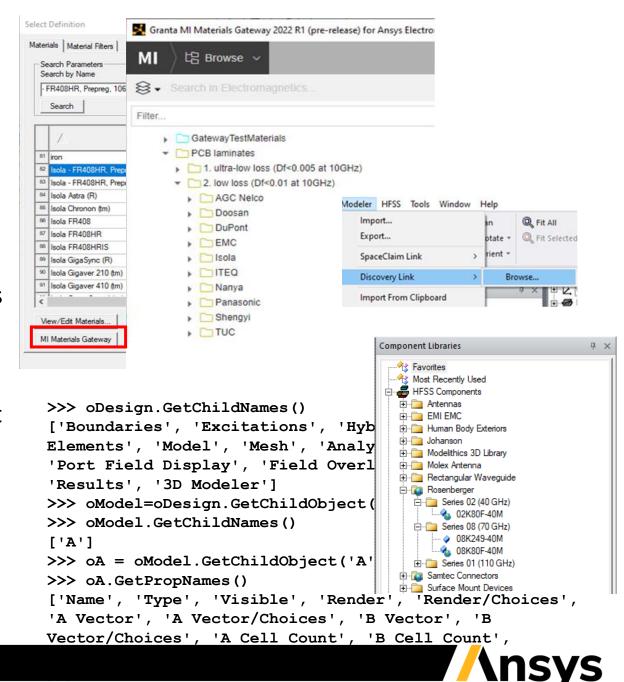

# **Ansys Electronics Desktop**

### **Ansys Electronics Desktop**

- Granta MI Materials Gateway

- Granta Material Gateway integrated in AEDT material browser

- 3D Component Agents

- Identical tree hierarchy as installed components

- Object oriented property scripting

- New modules: Mesh operations, 3D component array, Field overlays

- Functions to access SI and evaluated values

- 3D Modeler Discovery link (Beta)

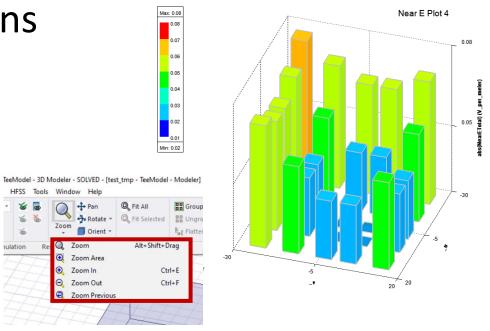

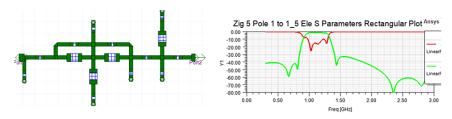

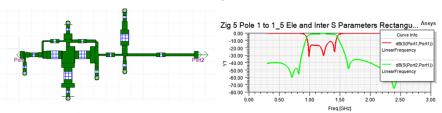

### Graphics, Post processing, FilterSolutions

- 3D Rectangular Bar plot type

- Enhanced zoom controls in 3D modeler and plots

- Improved handling of post-processing variables in Optimetrics

- Automated Discrete Optimization [Beta]

- Rapid and Accurate Lumped Element Filter Design

- Utilizes Ansys FilterSolutions, Circuits, and AEDT Optimizers

- Support for Modelithics Library

**First Pass Optimizes Only the Elements**

#### **Second Pass Optimizes Interconnects**

# **Ansys**